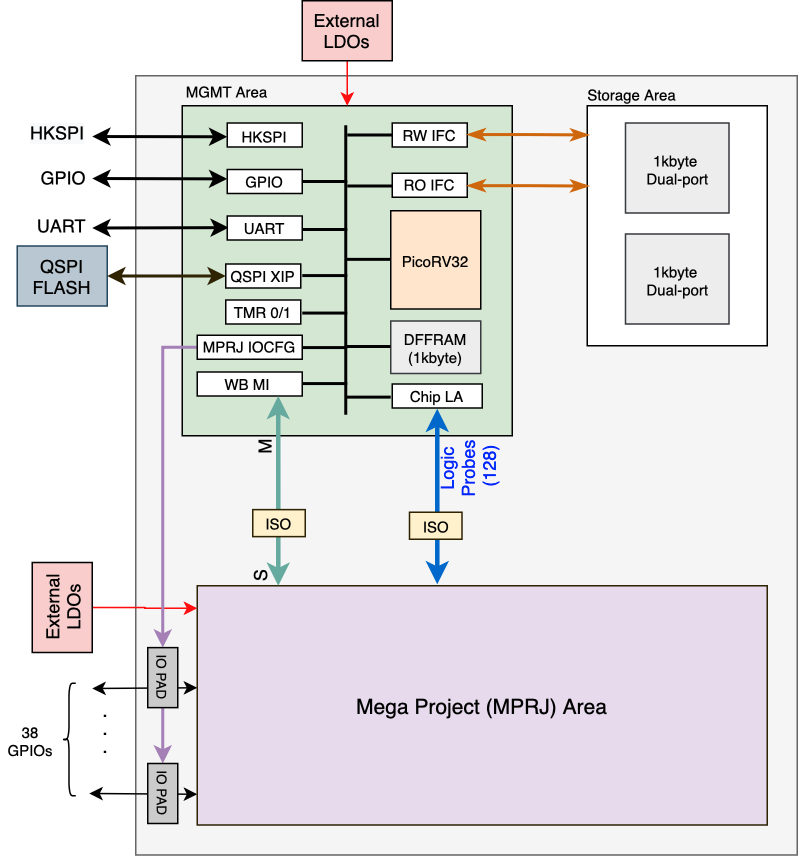

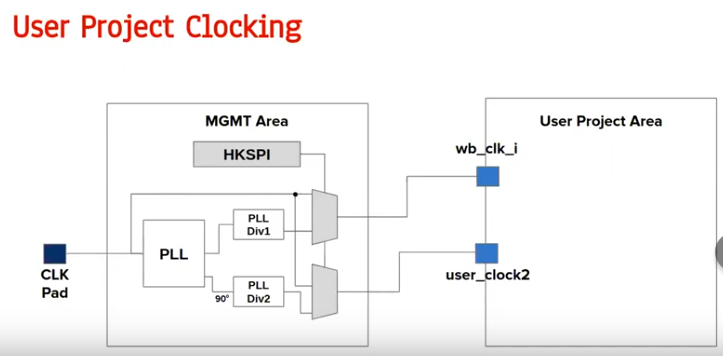

I was watching a few videos on Skywater's Caravel harness, and thought the lack of PLL in the preengineered section was a limitation. Turns out there is one, they just don't put it on the top-level block diagram!

But wait there's more! @The6P4C pointed out it's not a PLL, it's an FLL, based on a trimmable ring oscillator https://github.com/efabless/caravel/blob/master/verilog/rtl/digital_pll_controller.v

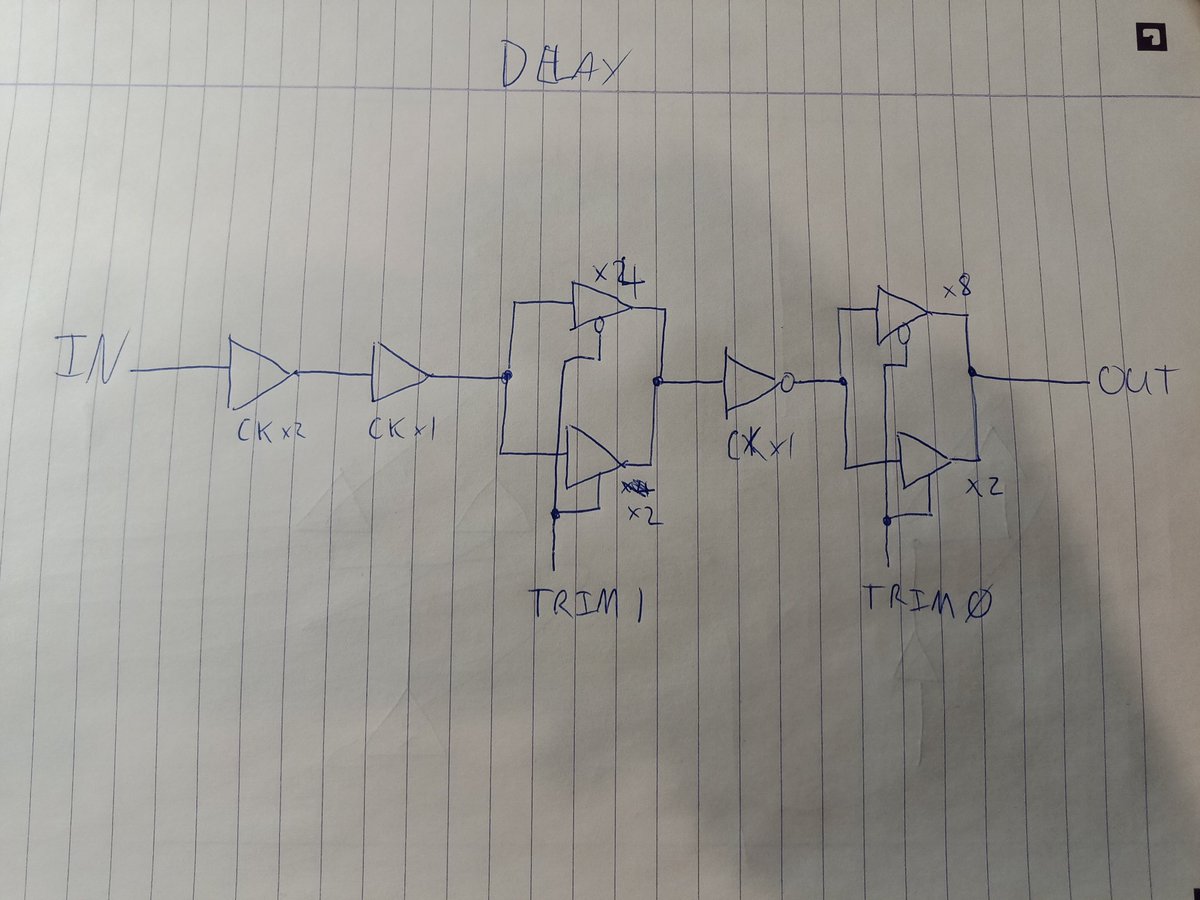

The ring oscillator is built from standard cells. Took me a while to find where to look up the cell names https://github.com/efabless/caravel/blob/c4c79cdf63d6a7ed7ceec4e0afbabe21fa5f9bfb/verilog/rtl/ring_osc2x13.v

Functionally it's an inverter. The number next to each cell is the drive strength.The trim bits select between tristate buffers of different drive strength, each of which drives the same capacitive load, so changing the trim bits changes the propagation delay of the stage.

You can see I got the strengths the wrong way round at first -- increasing the trim values actually slows the oscillator down. The source for the loop controller confirms this

trim[0] makes a bigger difference than trim[1] because you're exchanging a D8 buffer for a D2, instead of D4 for D2. Agrees with this comment in the ringosc source, and with the way they are generating the control codes.

Hey I know another chip that boots from a ring oscillator! This is how the one on RP2040 works. Similar principle, controlling drive strength into a constant load

Ours ends up running much faster (can go >1GHz if you fiddle with the range) but output is nasty and asymmetric because we don't use CK buffers, and don't invert between stages. Doesn't really matter -- just run it fast and use an output divider. Good enough to boot from

Clearly the biggest question is whether the skywater PLL/FLL thing can generate a DDR bit clock for TMDS, and whether the pads are fast enough!

Sinks are quite forgiving, but annoyingly you can't control the trim manually, so you can't stop the controller hunting around

Sinks are quite forgiving, but annoyingly you can't control the trim manually, so you can't stop the controller hunting around

Anyway the Skywater stuff looks awesome, I was watching some of Matthew Venn's videos last night. I love the idea of having a preengineered test harness with a processor and whatnot

Read on Twitter

Read on Twitter

![trim[0] makes a bigger difference than trim[1] because you're exchanging a D8 buffer for a D2, instead of D4 for D2. Agrees with this comment in the ringosc source, and with the way they are generating the control codes. trim[0] makes a bigger difference than trim[1] because you're exchanging a D8 buffer for a D2, instead of D4 for D2. Agrees with this comment in the ringosc source, and with the way they are generating the control codes.](https://pbs.twimg.com/media/EtrnxTsXAAAQ9m3.png)

![trim[0] makes a bigger difference than trim[1] because you're exchanging a D8 buffer for a D2, instead of D4 for D2. Agrees with this comment in the ringosc source, and with the way they are generating the control codes. trim[0] makes a bigger difference than trim[1] because you're exchanging a D8 buffer for a D2, instead of D4 for D2. Agrees with this comment in the ringosc source, and with the way they are generating the control codes.](https://pbs.twimg.com/media/Etrn6pcXUAEy1Xy.png)